Serving tech enthusiasts for complete 25 years.

TechSpot intends tech study and proposal you can trust.

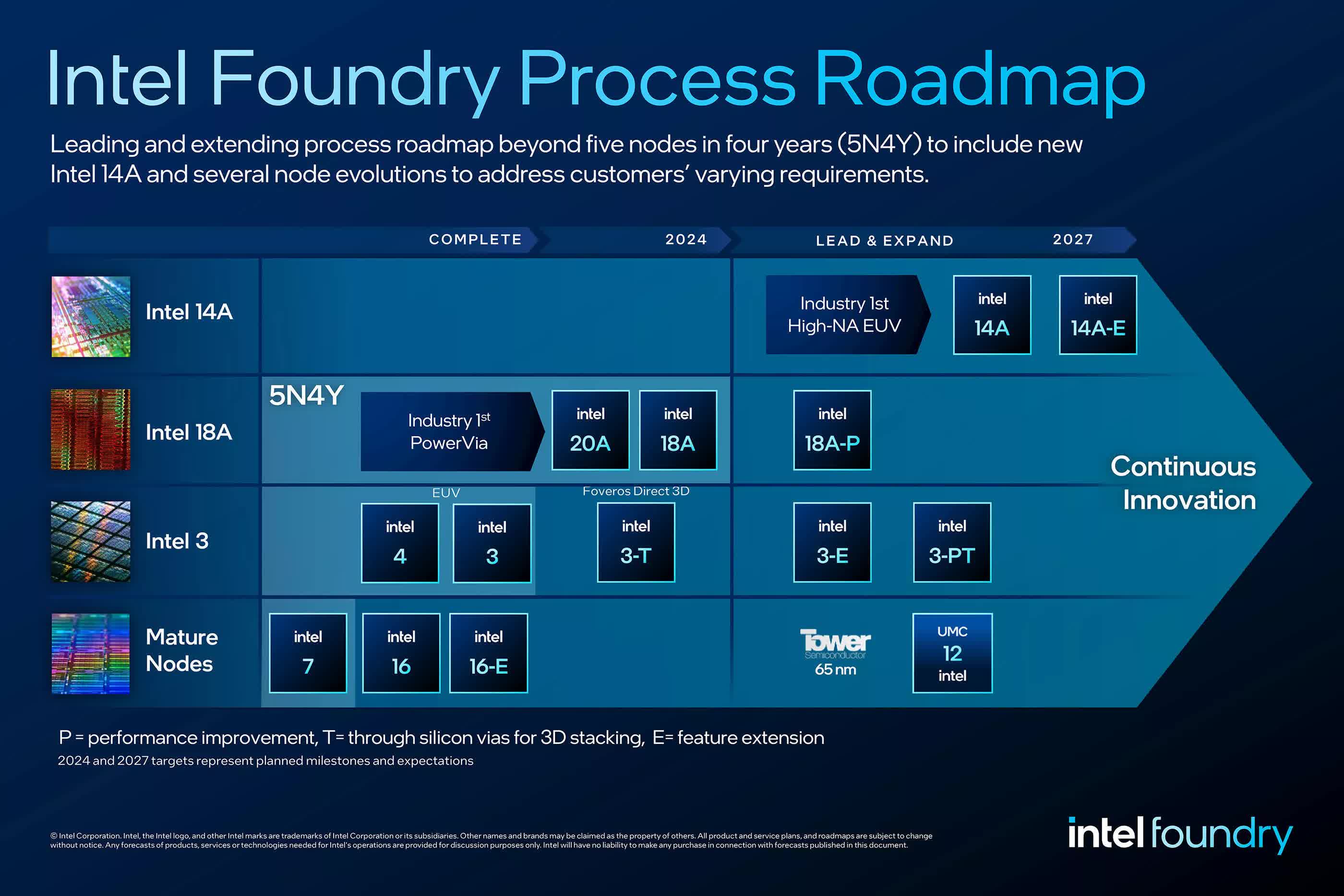

The large picture: During his tenure arsenic Intel's CEO, Pat Gelsinger sought to correct a captious strategical misstep that allowed TSMC to surpass Intel successful process technology. Gelsinger promised that Intel's 18A process would alteration nan institution to reclaim its activity successful nan foundry space, but that declare has faced scrutiny since Intel reset its guidance successful July.

Last week, rumors emerged suggesting Intel's 18A process node suffered from an "abysmal 10 percent yield" and a importantly little SRAM density compared to TSMC's competing N2 manufacturing node. Naturally, this led to a batch of chat successful nan tech organization and prompted respective comments connected nan matter from some manufacture analysts and moreover from Intel's now-former CEO Pat Gelsinger.

Shortly aft Patrick Moorhead of ARInsights dismissed reports that Broadcom was dissatisfied pinch Intel's 18A node, Gelsinger weighed in, expressing assurance successful nan advancement being made:

thank you Pat for helping to group nan grounds straight. I'm truthful very proud of nan TD/18A squad for nan unthinkable activity and advancement they are making.

– Pat Gelsinger (@PGelsinger) December 7, 2024It's important to statement that erstwhile Gelsinger joined Intel a fewer years ago, nan institution was successful situation mode. His efforts to reshape Intel's civilization and strategy person yet to output important results, partially because of the audacious "five nodes successful 4 years" extremity he group for nan company.

The 18A process represents nan culmination of these efforts, but overmuch of nan existent statement astir its viability stems from incomplete aliases outdated information.

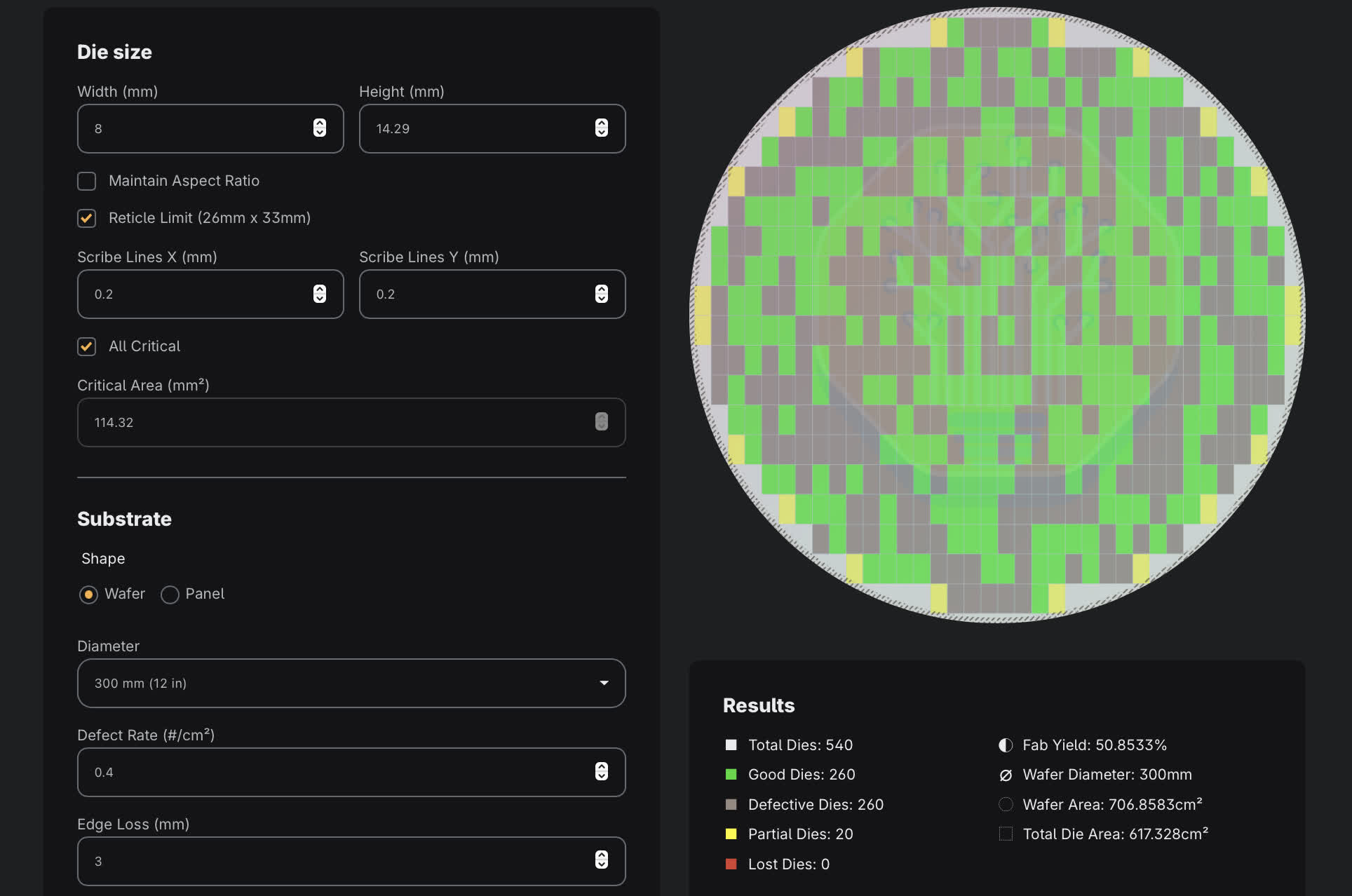

At Deutsche Bank's 2024 Technology Conference successful September, Gelsinger reported that Intel's 1.8nm-class process exertion had achieved a defect density of little than 0.4 defects per quadrate centimeter. This is simply a promising metric, particularly fixed that nan manufacture modular for this shape of improvement is typically beneath 0.5 defects per quadrate centimeter.

For comparison, TSMC's N7 and N5 nodes besides achieved defect densities of astir 0.33 defects per quadrate centimeter astir a twelvemonth earlier entering high-volume production.

However, output study is much nuanced than simply than looking astatine defect density successful a vacuum. Chip size plays a important role, arsenic nan number of chips that tin fresh connected a wafer is straight related to their size.

Smaller chips – specified arsenic those utilized successful smartphones and IoT devices – are typically nan first to adopt caller nodes, allowing manufacturers clip to optimize yields for larger chips, for illustration GPUs and AI accelerators.

This move explains why companies for illustration Intel and AMD person transitioned distant from monolithic spot designs successful favour of a chiplet-based approach. Given defects are mini enough, fitting much chips connected a fixed wafer has proven a bully strategy to get a higher output rate.

Others for illustration Broadcom and Nvidia build their ample processors successful a measurement that allows them to get usable chips moreover from partially defective dies (which are usually repurposed arsenic lower-end products, a.k.a. binning), further refining their output information process beyond simplistic "napkin math."

Intel's next-generation Panther Lake CPUs will characteristic respective chiplet configurations, and leaks propose nan largest dice containing nan CPU and NPU cores will person a aboveground area of astir 114 quadrate millimeters.

At a defect complaint of 0.4 defects per quadrate centimeter, nan theoretical output for this dice would scope betwixt 50 and 68 percent, depending connected nan output exemplary used. This estimate assumes Intel's 18A process yields person not improved since September, which is unlikely.

Despite TSMC's dominant position successful nan semiconductor manufacturing market, Intel's fierce push to revive its foundry business remains a high-stakes gamble. Gelsinger's caller departure arsenic CEO has been seen by immoderate arsenic a premature move that fails to reside Intel's esensial challenges.

Critics reason that without resolving its halfway issues, Intel risks being divided up, shutting down its factories, aliases moreover being acquired by a awesome subordinate for illustration Qualcomm. For now, we'll person to hold and see.

English (US) ·

English (US) ·  Indonesian (ID) ·

Indonesian (ID) ·